- บทที่ 1: นิยามและสถาปัตยกรรมทางกายภาพของ Secure Element

- โครงสร้างการป้องกันทางกายภาพ

- บทที่ 2: กลไกการทำงานของ Secure Element ใน Hardware Wallet

- 1. การสร้างกุญแจส่วนตัว (Key Generation) และการสร้างความสุ่ม

- 2. การเก็บรักษากุญแจในสภาวะ Cold Storage

- 3. กระบวนการลงนามธุรกรรมแบบแยกส่วน (Isolated Signing)

- การโจมตีผ่านช่องทางข้าง (Side-Channel Attacks)

- การฉีดความผิดพลาด (Fault Injection Attacks)

- บทที่ 4: การเปรียบเทียบ Secure Element กับแนวทางความปลอดภัยอื่น ๆ

- 1. Secure Element (SE) vs. ไมโครคอนโทรลเลอร์ทั่วไป (General-Purpose MCU)

- 2. Secure Element vs. Trusted Execution Environment (TEE)

- 3. Secure Element vs. TPM (Trusted Platform Module)

- บทที่ 5: มาตรฐานและการรับรองความปลอดภัย (Common Criteria & EAL)

- บทที่ 6: เจาะลึกการนำ Secure Element ไปใช้งานในแบรนด์ต่าง ๆ

- 1. แบรนด์ Ledger (Nano S Plus, Nano X, Stax, Flex)

- 2. แบรนด์ Trezor (Safe 3, Safe 5, Safe 7)

- 3. แบรนด์ Coldcard (MK4)

- บทที่ 7: ความสามารถพิเศษที่ Secure Element มอบให้กับ Hardware Wallet

- 1. การปกป้องหน้าจอ (Secure Screen)

- 2. การพิสูจน์ตัวตน FIDO2 และ U2F

- 3. โปรโตคอล Anti-Klepto

- บทที่ 8: สิ่งที่ Secure Element ทำไม่ได้ และข้อจำกัดที่ควรระวัง

- 1. การฟิชชิงและความประมาทของผู้ใช้งาน (Phishing & Human Error)

- 2. การสูญเสีย Seed Phrase ภายนอกอุปกรณ์

- 3. การลงนามแบบไม่เห็นข้อมูล (Blind Signing)

- 4. การวางยาที่อยู่กระเป๋า (Address Poisoning)

- บทที่ 9: อนาคตของ Secure Element และความโปร่งใสในฮาร์ดแวร์

- การเกิดขึ้นของ Open-Source Secure Element (TROPIC01)

- การรับมือกับ Quantum Computing

- บทสรุป

วิวัฒนาการของการจัดเก็บสินทรัพย์ดิจิทัลได้เดินทางมาถึงจุดที่ความปลอดภัยไม่ได้ขึ้นอยู่กับความแข็งแกร่งของรหัสผ่านเพียงอย่างเดียว แต่ขึ้นอยู่กับสถาปัตยกรรมทางกายภาพของอุปกรณ์ที่ใช้จัดเก็บ "กุญแจส่วนตัว" (Private Keys)

ในบริบทของคริปโตเคอร์เรนซี ข้อความที่ว่า "Not your keys, not your coins" ยังคงเป็นสัจนิรันดร์ที่เตือนใจนักลงทุนถึงความสำคัญของการครอบครองกุญแจด้วยตนเอง อย่างไรก็ตาม การครอบครองกุญแจส่วนตัวด้วยตนเองผ่าน Software Wallet บนคอมพิวเตอร์หรือสมาร์ทโฟนนั้นมาพร้อมกับความเสี่ยงมหาศาลจากมัลแวร์ การฟิชชิง และการโจมตีทางไซเบอร์ที่ซับซ้อน

ด้วยเหตุนี้ Hardware Wallet จึงถูกพัฒนาขึ้นเพื่อสร้างสภาวะแวดล้อมที่ "แยกตัวออกมา" (Isolated Environment) จากโลกอินเทอร์เน็ต และหัวใจสำคัญที่ทำหน้าที่เป็นปราการด่านสุดท้ายภายในอุปกรณ์เหล่านี้ก็คือชิปประมวลผลพิเศษที่เรียกว่า Secure Element (SE) ครับ

1: นิยามและสถาปัตยกรรมทางกายภาพของ Secure Element

Secure Element (SE) ไม่ใช่ไมโครชิปทั่วไปที่พบได้ในเครื่องใช้ไฟฟ้าหรือคอมพิวเตอร์ส่วนบุคคล แต่สิ่งนี้คือไมโครโพรเซสเซอร์เฉพาะทางที่ได้รับการออกแบบมาเพื่อวัตถุประสงค์เดียวคือการจัดเก็บและประมวลผลข้อมูลที่มีความอ่อนไหวสูงภายใต้สภาวะที่ต้านทานการโจมตีทั้งทางกายภาพและทางซอฟต์แวร์ หากจะเปรียบเทียบให้เห็นภาพ Hardware Wallet คือตู้เซฟทั้งใบ แต่ Secure Element คือ "กล่องนิรภัยภายในตู้เซฟ" ที่มีความหนาและระบบป้องกันซับซ้อนกว่าส่วนประกอบอื่นของตู้ครับ

ในทางเทคนิค SE เป็นชิปที่แยกออกมาทางกายภาพ (Discrete Hardware) ซึ่งทำงานอิสระจากชิปประมวลผลหลักหรือไมโครคอนโทรลเลอร์ (MCU) ของอุปกรณ์ ต้นกำเนิดของเทคโนโลยีนี้หยั่งรากลึกอยู่ในอุตสาหกรรมสมาร์ทการ์ด (Smart Cards) ที่ใช้ในบัตรเครดิต บัตรเดบิต ซิมการ์ดโทรศัพท์มือถือ และหนังสือเดินทางอิเล็กทรอนิกส์ (E-Passports) ความโดดเด่นของ SE คือการมีระบบปฏิบัติการขนาดเล็กภายในตัวเอง ซึ่งทำหน้าที่จำกัดการเข้าถึงข้อมูลและไม่อนุญาตให้มีการอ่านค่าข้อมูลลับออกจากหน่วยความจำโดยตรง

โครงสร้างการป้องกันทางกายภาพ

สิ่งที่ทำให้ SE แตกต่างจากชิปประมวลผลทั่วไปคือมาตรการป้องกันภายในระดับซิลิคอน ชิปเหล่านี้มักถูกติดตั้ง "ตาข่ายป้องกัน" (Protective Mesh) ซึ่งเป็นเลเยอร์ของวงจรไฟฟ้าที่คลุมส่วนประมวลผลและหน่วยความจำไว้ หากมีความพยายามที่จะเจาะพื้นผิวของชิปเพื่อใช้เครื่องมือวัดแรงดันไฟฟ้าหรือใช้เลเซอร์ยิงเพื่อสกัดข้อมูล ตาข่ายนี้จะขาดออกและส่งสัญญาณให้ชิปทำลายข้อมูลภายในทิ้งทันที (Self-destruction) นอกจากนี้ SE ยังถูกออกแบบให้มีความต้านทานต่อการวิศวกรรมย้อนกลับ (Reverse Engineering) และการวิเคราะห์การไหลของกระแสไฟฟ้าที่เป็นความลับ

2: กลไกการทำงานของ Secure Element ใน Hardware Wallet

หน้าที่หลักของ Secure Element ภายใน Hardware Wallet สามารถแบ่งออกเป็นขั้นตอนสำคัญที่ทำให้มั่นใจได้ว่ากุญแจส่วนตัวจะไม่ถูกเปิดเผยต่อโลกภายนอกแม้แต่เสี้ยววินาทีเดียว คือ

2.1. การสร้างกุญแจส่วนตัว (Key Generation) และการสุ่ม

พื้นฐานของความปลอดภัยในโลกคริปโตคือ ความสุ่ม (Entropy) หากกุญแจถูกสร้างขึ้นด้วยอัลกอริทึมที่สามารถคาดเดาได้ แฮ็กเกอร์จะสามารถคำนวณย้อนกลับเพื่อหา ชุดคำศัพท์ (Seed Phrase) ได้

SE แก้ปัญหานี้ด้วยการใช้ตัวสร้างตัวเลขสุ่มแบบฮาร์ดแวร์ที่แท้จริง (True Random Number Generator - TRNG) ซึ่งอาศัยปรากฏการณ์ทางฟิสิกส์ภายในวงจรไฟฟ้าเพื่อสร้างค่าที่ไม่มีรูปแบบตายตัว กระบวนการสร้างกุญแจส่วนตัวทั้งหมดจะเกิดขึ้นภายใน SE และจะถูกบันทึกไว้ในหน่วยความจำที่ถูกเข้ารหัส (Encrypted Memory) ของชิปนั้นเท่านั้น

2.2. การเก็บรักษากุญแจในสภาวะ Cold Storage

เมื่อกุญแจส่วนตัวถูกสร้างขึ้น มันจะถูกกักขังอยู่ภายในอาณาเขตของ SE ตลอดไป กุญแจนี้จะไม่ถูกดึงออกมาที่แรม (RAM) ของคอมพิวเตอร์ หรือแม้แต่แรมของตัวประมวลผลหลักในฮาร์ดแวร์วอลเล็ตเอง สภาวะนี้คือการทำ Cold Storage ที่แท้จริง เพราะกุญแจถูกแยกขาดจากซอฟต์แวร์ที่เชื่อมต่อกับอินเทอร์เน็ต

2.3. กระบวนการลงนามธุรกรรมแบบแยกส่วน (Isolated Signing)

เมื่อผู้ใช้งานต้องการทำธุรกรรม ขั้นตอนจะไม่ใช่การส่งกุญแจออกมาเพื่อเซ็นชื่อในคอมพิวเตอร์ แต่เป็นการส่ง "รายละเอียดธุรกรรมที่ยังไม่ได้ลงนาม" (Unsigned Transaction) เข้าไปใน SE ผ่านอินเทอร์เฟซที่จำกัด

- ขั้นตอนที่ A: แอปพลิเคชันบนคอมพิวเตอร์สร้างรายละเอียดธุรกรรม (เช่น ส่ง 1 BTC ไปที่ที่อยู่ X)

- ขั้นตอนที่ B: ข้อมูลนี้ถูกส่งเข้าสู่ฮาร์ดแวร์วอลเล็ต

- ขั้นตอนที่ C: Secure Element รับข้อมูลธุรกรรม และใช้กุญแจส่วนตัวที่เก็บไว้ภายในทำการคำนวณทางคณิตศาสตร์เพื่อสร้าง "ลายเซ็นดิจิทัล" (Digital Signature)

- ขั้นตอนที่ D: ลายเซ็นดิจิทัลถูกส่งกลับออกไปยังคอมพิวเตอร์เพื่อกระจายเข้าสู่เครือข่ายบล็อกเชน

ในเชิงคณิตศาสตร์ กระบวนการนี้ใช้หลักการของ Elliptic Curve Cryptography (ECC) โดยเฉพาะอัลกอริทึม ECDSA (เช่น บนเครือข่าย Bitcoin และ Ethereum)

บทที่ 3: ภัยคุกคามทางกายภาพและการป้องกันโดย Secure Element

เหตุผลหลักที่ Hardware Wallet ส่วนใหญ่เลือกใช้ SE แทนที่จะใช้ไมโครคอนโทรลเลอร์ (MCU) ทั่วไป คือความสามารถในการรับมือกับการโจมตีเมื่อแฮ็กเกอร์มี "ตัวเครื่อง Hardware Wallet" อยู่ในครอบครอง (Physical Attacks)

การโจมตีทางอ้อม (Side-Channel Attacks)

นี่คือหนึ่งในการโจมตีที่ซับซ้อนที่สุด โดยแฮ็กเกอร์ไม่ได้เจาะผ่านโค้ดโปรแกรม แต่ใช้การสังเกต "ร่องรอยทางกายภาพ" ของชิปขณะประมวลผลกุญแจส่วนตัว

- Power Analysis: การวัดความแตกต่างของการใช้พลังงานไฟฟ้าในระดับมิลลิแอมป์ขณะชิปประมวลผลบิตข้อมูลที่ต่างกัน หากเป็นชิปทั่วไป การคำนวณบิต "1" อาจใช้ไฟมากกว่าบิต "0" เล็กน้อย ซึ่งแฮ็กเกอร์สามารถใช้สถิติรวบรวมข้อมูลจนสกัดกุญแจออกมาได้

- Electromagnetic Leakage: ชิปทุกตัวจะแผ่รังสีแม่เหล็กไฟฟ้าออกมาขณะทำงาน SE ถูกออกแบบมาให้มีเกราะกำจัดคลื่นเหล่านี้หรือสร้าง "สัญญาณรบกวน" (Noise) เพื่อพรางข้อมูลจริง

SE ปกป้องข้อมูลด้วยเทคนิค Constant Time Execution (การทำให้ทุกคำสั่งใช้เวลาเท่ากันไม่ว่าข้อมูลจะเป็นอะไร) และ Power Flattening (การเพิ่มการใช้ไฟปลอม ๆ เข้าไปเพื่อให้กราฟการใช้ไฟดูราบเรียบเสมอ) ทำให้แฮ็กเกอร์ไม่สามารถแยกแยะข้อมูลลับออกจากสัญญาณรบกวนได้

การฉีดความผิดพลาด (Fault Injection Attacks)

แฮ็กเกอร์อาจพยายามทำให้เกิด "ความปั่นป่วน" ในการทำงานของชิป เช่น การทำ Voltage Glitching หรือการลดแรงดันไฟฟ้ากระทันหันในช่วงเวลาเพียงไม่กี่นาโนวินาที เพื่อให้ชิป "ข้าม" คำสั่งตรวจสอบความปลอดภัย (เช่น ข้ามขั้นตอนการเช็ก PIN) ชิป SE มีเซนเซอร์ตรวจจับแรงดันไฟฟ้าและความถี่ที่ละเอียดมาก หากพบความผิดปกติเพียงเล็กน้อย มันจะหยุดการประมวลผลหรือรีเซ็ตตัวเองทันที

| ประเภทการโจมตี | เป้าหมายของการโจมตี | กลไกการป้องกันของ SE |

|---|---|---|

| Simple Power Analysis (SPA) | ตรวจจับรูปแบบกุญแจจากการใช้ไฟครั้งเดียว | การสุ่มลำดับคำสั่งและสร้างสัญญาณรบกวนไฟ |

| Differential Power Analysis (DPA) | ใช้สถิติจากการใช้ไฟหลายครั้งเพื่อหาค่ากุญแจ | การใช้ Masking และ Blinding ทางคณิตศาสตร์ |

| Clock Glitching | บังคับให้ข้ามคำสั่งสำคัญด้วยสัญญาณนาฬิกาผิดปกติ | ตัวสร้างสัญญาณนาฬิกาภายในที่ควบคุมอิสระ |

| Laser Fault Injection | ใช้เลเซอร์เหนี่ยวนำให้บิตข้อมูลในหน่วยความจำเปลี่ยนค่า | ตาข่ายป้องกันแสงและเซนเซอร์ตรวจจับแสงภายในชิป |

| Cold-Boot Attack | การแช่แข็งแรมเพื่อดึงข้อมูลที่ค้างอยู่หลังจากปิดเครื่อง | หน่วยความจำที่ถูกเข้ารหัสและไม่มีข้อมูลค้างในแรมหลัก |

4: การเปรียบเทียบ Secure Element กับแนวทางความปลอดภัยอื่น ๆ

ในตลาดและวงการ Hardware Wallet มีการถกเถียงกันอย่างกว้างขวางเกี่ยวกับความจำเป็นของ SE เมื่อเทียบกับสถาปัตยกรรมแบบอื่น การเข้าใจความแตกต่างเหล่านี้จะช่วยให้นักลงทุนเลือกอุปกรณ์ที่เหมาะสมกับระดับความเสี่ยงของตนเองได้ครับ

4.1. Secure Element (SE) vs. ไมโครคอนโทรลเลอร์ทั่วไป (General-Purpose MCU)

ไมโครคอนโทรลเลอร์อย่าง STM32 (ที่ใช้ใน Trezor รุ่นเก่า) เป็นชิปอเนกประสงค์ที่ออกแบบมาเพื่อความเร็วและประสิทธิภาพ ไม่ใช่เพื่อความปลอดภัยทางกายภาพ แม้ว่าจะสามารถเขียนโปรแกรมให้ปลอดภัยได้ในระดับซอฟต์แวร์ แต่หากแฮ็กเกอร์เข้าถึงตัวเครื่องได้ พวกเขาสามารถใช้วิธี Voltage Glitching เพื่อ "Dump" ข้อมูลใน Flash Memory ออกมาและสกัดกุญแจส่วนตัวได้ภายในเวลาไม่นาน

4.2. Secure Element vs. Trusted Execution Environment (TEE)

TEE เป็นโซลูชันที่ใช้ในสมาร์ทโฟนสมัยใหม่ (เช่น Apple Enclave หรือ ARM TrustZone) ซึ่งสร้าง "โลกคู่ขนาน" ที่ปลอดภัยภายในชิปประมวลผลหลัก แม้ TEE จะดีกว่า MCU ทั่วไป แต่เนื่องจากมันยังคงแชร์ทรัพยากรบางส่วน (เช่น บัสข้อมูลและแหล่งจ่ายไฟ) กับระบบปฏิบัติการหลัก มันจึงมีความเสี่ยงต่อการโจมตีประเภท Side-channel มากกว่า SE ที่แยกออกมาเป็นเอกเทศอย่างสมบูรณ์

4.3. Secure Element vs. TPM (Trusted Platform Module)

TPM มักพบในแล็ปท็อปเพื่อใช้ในการตรวจสอบความถูกต้องของระบบบูตและเก็บกุญแจเข้ารหัสไฟล์ อย่างไรก็ตาม TPM ถูกออกแบบมาตามมาตรฐานอุตสาหกรรมคอมพิวเตอร์ทั่วไป ซึ่งอาจไม่มีความต้านทานต่อการโจมตีทางกายภาพในระดับที่สูงเท่ากับ SE ที่ได้รับการรับรองระดับ EAL5+ หรือ EAL6+ ที่ใช้ในวอลเล็ตคริปโตโดยเฉพาะ

5: มาตรฐานและการรับรองความปลอดภัย (Common Criteria & EAL)

ในการประเมินประสิทธิภาพของ Secure Element อุตสาหกรรมได้นำมาตรฐานสากลที่เรียกว่า Common Criteria (ISO/IEC 15408) มาใช้ ซึ่งจะกำหนดระดับที่เรียกว่า Evaluation Assurance Level (EAL)

- EAL1 - EAL4: เหมาะสำหรับระบบที่ไม่ได้เผชิญกับการโจมตีทางกายภาพที่ซับซ้อน

- EAL5+: เป็นมาตรฐานระดับสูงที่ใช้ในบัตรเครดิตและหนังสือเดินทางอิเล็กทรอนิกส์ ชิปในระดับนี้ถูกทดสอบให้ต้านทานการโจมตีระดับสูงจากผู้เชี่ยวชาญได้

- EAL6+: เป็นระดับความมั่นใจที่สูงขึ้นไปอีก มักพบในชิปรุ่นใหม่ ๆ เช่น Infineon OPTIGA Trust M ที่ใช้ใน Trezor Safe 5 ซึ่งผ่านการตรวจสอบในระดับที่เข้มงวดมากขึ้น

เครื่องหมาย "+" (เช่น EAL5+) หมายถึงชิปนั้นผ่านข้อกำหนดเพิ่มเติมในบางหัวข้อที่สำคัญต่อความปลอดภัย เช่น การป้องกันการฉีดความผิดพลาด (Fault Injection) ที่เกินกว่ามาตรฐานทั่วไปกำหนด

6: เจาะลึกการนำ Secure Element ไปใช้งานในแบรนด์ต่าง ๆ

แต่ละแบรนด์มีแนวคิดในการผสานรวม SE เข้ากับอุปกรณ์ที่แตกต่างกัน ซึ่งสะท้อนถึงปรัชญาความปลอดภัยที่ต่างกันด้วย

6.1. แบรนด์ Ledger (Nano S Plus, Nano X, Stax, Flex)

Ledger เป็นผู้บุกเบิกการใช้ SE ในฮาร์ดแวร์วอลเล็ต โดยใช้ชิปตระกูล ST33 จาก STMicroelectronics

- รุ่นชิป: ST33J2M0 หรือรุ่นที่ใกล้เคียง ซึ่งได้รับการรับรอง EAL5+ หรือ EAL6+

- จุดเด่น: Ledger ใช้ SE เป็นหัวใจหลักในการรันระบบปฏิบัติการ BOLOS และควบคุมหน้าจอ (Secure Screen) โดยตรง ทำให้มั่นใจได้ว่าข้อมูลที่ปรากฏบนหน้าจอไม่ถูกแทรกแซงจากมัลแวร์

- ข้อจำกัด: เนื่องจากข้อตกลงไม่เปิดเผยข้อมูล (NDA) กับผู้ผลิตชิป ทำให้ซอร์สโค้ดในส่วนของชิป SE ไม่สามารถเปิดเผยต่อสาธารณะได้ทั้งหมด

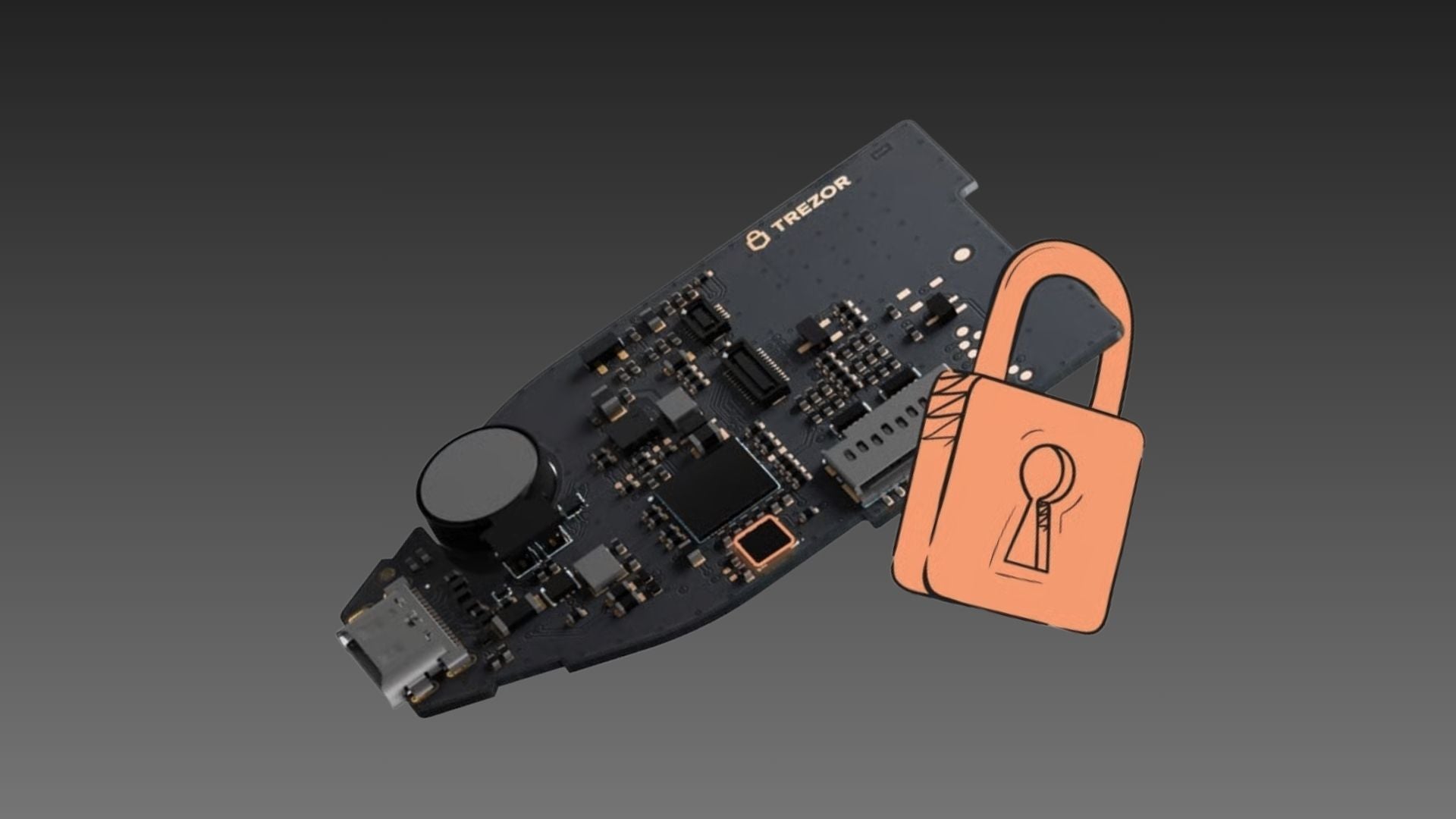

6.2. แบรนด์ Trezor (Safe 3, Safe 5, Safe 7)

Trezor เคยยึดถือแนวทาง Open-source 100% ทำให้รุ่นก่อนหน้า (Model One, Model T) ไม่ใช้ SE เพราะหาชิปที่เปิดเผยพิมพ์เขียวไม่ได้ แต่ในยุคใหม่ Trezor ได้เปลี่ยนสถาปัตยกรรมเพื่ออุดช่องโหว่ทางกายภาพ

- Trezor Safe 3 & 5: ใช้ชิป Infineon OPTIGA Trust M (V3) ซึ่งเป็นชิป EAL6+ ที่ไม่มีเงื่อนไข NDA ที่เข้มงวด ทำให้ Trezor ยังคงสามารถเปิดเผยรายละเอียดการทำงานส่วนใหญ่ได้

- Trezor Safe 7: นำเสนอเทคโนโลยี TROPIC01 ซึ่งเป็นชิป SE ตัวแรกของโลกที่พัฒนาขึ้นภายใต้แนวคิด Truly Open Integrated Circuit โดยบริษัท Tropic Square (บริษัทในเครือ SatoshiLabs) เพื่อสร้างมาตรฐานใหม่ที่ทั้งปลอดภัยระดับ SE และสามารถตรวจสอบได้ (Auditable)

6.3. แบรนด์ Coldcard (MK4)

Coldcard เป็นแบรนด์ที่เน้นกลุ่มผู้ใช้งาน Bitcoin ระดับสูง (Bitcoin-only) และยกระดับความปลอดภัยด้วยชิป SE คู่

- ชิปคู่: ใช้ทั้ง Microchip ATECC608B และ Maxim DS28C36B

- ปรัชญา: การมี SE สองตัวจากสองผู้ผลิตช่วยป้องกันความเสี่ยงที่แฝงมากับห่วงโซ่อุปทาน (Supply Chain Risk) หากมีช่องโหว่ลับในชิปตัวหนึ่ง อีกตัวหนึ่งจะยังคงทำหน้าที่ปกป้องกุญแจไว้ได้ นอกจากนี้ Coldcard ยังมีฟังก์ชัน "Shoot This" ซึ่งบอกตำแหน่งที่ตั้งของชิป SE อย่างชัดเจนเพื่อให้ผู้ใช้สามารถทำลายชิปทิ้งได้ทันทีด้วยสว่านหากเกิดสถานการณ์ฉุกเฉิน

| คุณสมบัติ | Ledger Nano X | Trezor Safe 5 | Coldcard MK4 |

|---|---|---|---|

| Secure Element Model | ST33J2M0 | OPTIGA Trust M | Dual: ATECC608B + DS28C36B |

| Certification Level | CC EAL5+ | CC EAL6+ | N/A (Chip only) |

| Open-source (Software) | Partial | Fully Open | Fully Open |

| Open-source (Hardware) | No | No (except Safe 7) | No |

| Anti-Klepto Support | No | No | Yes (Partial) |

| การเชื่อมต่อหลัก | Bluetooth/USB-C | USB-C | Air-gapped/MicroSD |

7: ความสามารถพิเศษที่ Secure Element มอบให้กับ Hardware Wallet

นอกเหนือจากการเก็บกุญแจคริปโต SE ยังขยายขอบเขตการทำงานไปสู่มาตรฐานความปลอดภัยสากลอื่น ๆ

7.1. การปกป้องหน้าจอ (Secure Screen)

ในอุปกรณ์อย่าง Ledger หน้าจอจะถูกควบคุมโดยตรงจาก Secure Element นี่คือจุดตายที่สำคัญมาก เพราะหากหน้าจอถูกควบคุมโดย MCU ทั่วไป มัลแวร์ในเครื่องคอมพิวเตอร์อาจจะส่งคำสั่งไปหลอกหน้าจอวอลเล็ตให้แสดงผลที่อยู่กระเป๋าที่ถูกต้อง แต่ในความเป็นจริงกำลังลงนามธุรกรรมไปยังที่อยู่ของแฮ็กเกอร์ SE จะป้องกันเรื่องนี้ด้วยการดึงข้อมูลจากหน่วยความจำที่ปลอดภัยมาแสดงผลโดยตรง

7.2. การพิสูจน์ตัวตน FIDO2 และ U2F

SE สามารถเปลี่ยนฮาร์ดแวร์วอลเล็ตให้กลายเป็น "กุญแจความปลอดภัยทางกายภาพ" (Security Key) สำหรับล็อกอิน Google, Facebook, หรือ Dropbox ได้ มาตรฐาน FIDO2 ใช้กุญแจสาธารณะ (Public Key Cryptography) ภายใน SE เพื่อยืนยันว่าผู้ใช้งานมีอุปกรณ์จริงอยู่กับตัว ป้องกันการถูกแฮ็กบัญชีจาก Phishing ได้เกือบ 100% เพราะแฮ็กเกอร์ไม่มีกุญแจส่วนตัวที่ฝังอยู่ในชิป SE ของคุณ

7.3. โปรโตคอล Anti-Klepto

ความกังวลอย่างหนึ่งคือ "ช่องโหว่ลับ" ในเฟิร์มแวร์วอลเล็ตที่อาจแอบส่งกุญแจส่วนตัวออกมาผ่านลายเซ็นธุรกรรม (Nonce Covert Channel) โดยปกติลายเซ็นธุรกรรมต้องการค่า Nonce ซึ่งต้องเป็นความลับและสุ่ม

หากแฮ็กเกอร์สามารถควบคุม Nonce ได้ พวกเขาสามารถทำให้กุญแจส่วนตัวของคุณรั่วไหลออกไปทางบล็อกเชนโดยที่คุณไม่รู้ตัว โปรโตคอล Anti-Klepto (หรือที่เรียกว่า Sign-to-Contract) จะบังคับให้ SE และคอมพิวเตอร์ร่วมกันสร้างค่า Nonce นี้ขึ้นมา เพื่อให้มั่นใจว่าจะไม่มีฝ่ายใดฝ่ายหนึ่งสามารถแอบฝังข้อมูลลับลงไปในลายเซ็นได้

หากคุณจด 24 คำ (Recovery Phrase) ลงในกระดาษ แล้วมีคนมาแอบถ่ายรูปกระดาษใบนั้นไป แฮ็กเกอร์สามารถกู้คืนวอลเล็ตของคุณในอุปกรณ์อื่นได้ทันทีโดยไม่ต้องผ่าน SE ในวอลเล็ตตัวเครื่องเลย SE ป้องกันได้เฉพาะ "การดึงข้อมูลจากตัวชิป" แต่ไม่สามารถป้องกัน "ข้อมูลที่รั่วไหลไปแล้วในรูปแบบอื่น"

8: สิ่งที่ Secure Element ทำไม่ได้ และข้อจำกัดที่ควรระวัง

8.3. การลงนามแบบไม่เห็นข้อมูล (Blind Signing)

แม้ว่า SE จะเป็นเทคโนโลยีที่ยอดเยี่ยม แต่มันไม่ใช่คำตอบสำหรับทุกปัญหาความปลอดภัย มีช่องโหว่หลายอย่างที่ SE ไม่สามารถป้องกันได้เนื่องจากอยู่นอกขอบเขตการทำงานของฮาร์ดแวร์

8.1. การฟิชชิงและความประมาทของผู้ใช้งาน (Phishing & Human Error)

SE มีหน้าที่ลงนามธุรกรรมตามที่ได้รับคำสั่ง หากมิจฉาชีพสร้างเว็บไซต์ปลอมที่ดูเหมือน Uniswap และหลอกให้คุณกด "ลงนาม" (Sign) ในธุรกรรมที่อนุญาตให้พวกเขาดึงเงินออกไป (Approve) SE จะทำตามคำสั่งนั้นอย่างซื่อสัตย์ เมื่อธุรกรรมเกิดขึ้นบนบล็อกเชนแล้ว SE ไม่สามารถเรียกคืนเงินกลับมาได้

8.2. การสูญเสีย Seed Phrase ภายนอกอุปกรณ์

ในการใช้งานสมาร์ทคอนแทร็กต์ (Smart Contracts) ที่ซับซ้อน หน้าจอวอลเล็ตบางรุ่นไม่สามารถแปลงข้อมูลดิบ (Data Hex) เป็นภาษาที่มนุษย์อ่านออกได้ อุปกรณ์อาจจะแสดงเพียงคำว่า "Data Present" หรือรหัสยาว ๆ การกดยืนยันในสภาวะนี้เรียกว่า Blind Signing ซึ่งเปรียบเสมือนการ "เซ็นเช็คเปล่า" SE จะทำการเซ็นสัญญาให้ทันทีตามที่คุณกด โดยที่ไม่รู้ว่าสัญญานั้นคือการฝากเงินหรือการยกเลิกสิทธิ์ในการครอบครองทรัพย์สินของคุณ

8.4. การวางยาที่อยู่กระเป๋า (Address Poisoning)

นี่คือกลโกงที่มิจฉาชีพส่งธุรกรรมมูลค่า 0 บาทมาให้คุณ โดยใช้ที่อยู่ที่ "หน้าตาคล้าย" กับที่อยู่ประจำของคุณ เพื่อหลอกให้คุณก๊อปปี้ที่อยู่นั้นจากประวัติธุรกรรมเพื่อใช้โอนเงินในครั้งต่อไป SE ไม่สามารถรู้ได้ว่าที่อยู่ที่คุณก๊อปปี้มานั้นเป็นที่อยู่ของเพื่อนคุณหรือของแฮ็กเกอร์

9: อนาคตของ Secure Element และความโปร่งใสในฮาร์ดแวร์

อุตสาหกรรมฮาร์ดแวร์วอลเล็ตกำลังเผชิญกับจุดเปลี่ยนสำคัญในการเลือกระหว่าง "ความลับของผู้ผลิต" และ "ความโปร่งใสที่ตรวจสอบได้"

การเกิดขึ้นของ Open-Source Secure Element (TROPIC01)

บริษัท Tropic Square ภายใต้การนำของ Jan Pleskač ได้เปิดตัวชิป TROPIC01 ซึ่งใช้สถาปัตยกรรม RISC-V และเป็น Open-architecture ทั้งหมด ความหมายของมันคือ:

- Auditability: ผู้เชี่ยวชาญทั่วโลกสามารถอ่านแผนผังวงจร (Netlist) ของชิปเพื่อตรวจสอบว่าไม่มีช่องโหว่หรือฟังก์ชันแอบแฝง

- No NDA: นักพัฒนาไม่ต้องเซ็นสัญญาปิดปาก ทำให้สามารถแจ้งเตือนช่องโหว่สู่สาธารณะได้อย่างรวดเร็ว

- Kerckhoffs's Principle: ความปลอดภัยต้องขึ้นอยู่กับ "ความลับของกุญแจ" ไม่ใช่ "ความลับของกระบวนการ" ซึ่งเป็นหลักการพื้นฐานของวิทยาการรหัสลับสมัยใหม่

การรับมือกับ Quantum Computing

แม้ว่าคอมพิวเตอร์ควอนตัมจะยังไม่สามารถทำลาย ECDSA ได้ในวันนี้ แต่ชิป SE รุ่นใหม่อย่าง TROPIC01 ได้ถูกออกแบบมาให้มีสถาปัตยกรรมแบบ Quantum-ready เพื่อเตรียมพร้อมรับมือกับการเปลี่ยนแปลงของอัลกอริทึมเข้ารหัสในอนาคต

บทสรุป

จากการวิเคราะห์เชิงลึกทั้งหมดข้างต้น เราสามารถสรุปประเด็นสำคัญเพื่อเป็นแนวทางในการเลือกและใช้งาน Hardware Wallet ที่มี Secure Element ได้ดังนี้ครับ

ความสำคัญของ SE คือ สำหรับผู้ที่ต้องการจัดเก็บสินทรัพย์ที่มีมูลค่าสูงและต้องการความปลอดภัยจากการขโมยตัวเครื่อง การเลือกวอลเล็ตที่มี Secure Element (ระดับ EAL5+ ขึ้นไป) เป็นสิ่งที่ "ต้องมี" (Must-have) ไม่ใช่แค่ทางเลือกครับ

- ความสมดุลระหว่าง Trust และ Verification

หากคุณเชื่อมั่นในบริษัทขนาดใหญ่ที่มีชื่อเสียงยาวนาน แบรนด์อย่าง Ledger ที่ใช้ชิปปิดแต่ได้รับการรับรองระดับสูงเป็นตัวเลือกที่มั่นใจได้ แต่หากคุณยึดถือปรัชญา "Don't Trust, Verify" แบรนด์ที่ใช้ชิปคู่หรือชิปแบบเปิดอย่าง Trezor Safe 3, 5, 7 หรือ ColdCard คือคำตอบ

- การใช้งานที่ถูกวิธี

Secure Element เป็นเพียงเครื่องมือหนึ่ง ความปลอดภัยที่แท้จริงเกิดจากการใช้งานที่รอบคอบ ได้แก่

- การตรวจสอบที่อยู่กระเป๋าบนหน้าจอวอลเล็ต (Trusted Display) ทุกครั้งก่อนกดปุ่ม

- การหลีกเลี่ยง Blind Signing ในโปรเจกต์ที่ไม่คุ้นเคย

- การเก็บรักษา Seed Phrase ในรูปแบบออฟไลน์และปลอดภัยที่สุด

- ความตระหนักรู้ต่อภัยคุกคามใหม่

แม้จะมี SE แต่การโจมตีอย่าง Address Poisoning หรือ Phishing ยังคงเป็นภัยคุกคามอันดับหนึ่งในปัจจุบัน การมีความรู้เท่าทันมิจฉาชีพจึงสำคัญไม่แพ้เทคโนโลยีชิป

ในท้ายที่สุด Secure Element คือเทคโนโลยีที่เปลี่ยน Hardware Wallet จากเพียงไดรฟ์เก็บข้อมูลธรรมดาให้กลายเป็น "ป้อมปราการดิจิทัล" ที่ช่วยให้เราสามารถนอนหลับได้อย่างสบายใจท่ามกลางสมรภูมิไซเบอร์ที่ดุเดือดในโลกของคริปโตเคอร์เรนซี การเลือกใช้ฮาร์ดแวร์วอลเล็ตที่มี SE จึงเป็นการลงทุนที่คุ้มค่าที่สุดเพื่อปกป้องอิสรภาพทางการเงินของคุณในระยะยาวครับ

Share:

เจาะลึกหน้าที่ Secure Element ใน OneKey